## دراسة إمكانية تخفيض الاستطاعة المستهلكة في دارات CMOS بإنقاص فعالية التبديل

$^{1}$  أحلام محمود محمود

(تاريخ الإيداع 1 / 3 / 2018. قُبِل للنشر في 2/ 5 / 2018)

## □ ملخّص □

يهدف البحث إلى دراسة تخفيض الاستطاعة المستهلكة في الدارات الرقمية نوع CMOS وإلى تطوير طرق جديدة في هذا المجال والحصول على نتائج عملية جديدة قابلة للتطبيق في مجال تطوير الأجهزة الإلكترونية المتكاملة عالية الاندماج VLSI ، تم في هذا البحث دراسة تخفيض الاستطاعة المستهلكة الديناميكية بتخفيض فعالية التبديل حيث تم تغيير البنية الهندسية للدارة الرقمية على الاستطاعة المستهلكة ، واستخدمت تراكيب مختلفة للدارة. حيث تم الحصول على نتائج جيدة بطريقة المحاكاة باستخدام برنامج ال Matlab حيث تم تخفيض قدره 10 %مما يساعد في تحقيق مواصفات عالية في تصميم الدارات.

الكلمات المفتاحية: فعالية التبديل -الاستطاعة المستهلكة - دارات CMOS

ahlamhisham@gmail.com ماجستير في هندسة الاتصالات والالكترونيات، كلية الهندسة الكهربائية والميكانيكية، جامعة تشرين

مجلة جامعة تشرين للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (40) العدد (3) Tishreen University Journal for Research and Scientific Studies - Engineering Sciences Series Vol. (40) No. (3) 2018

# The studying of reduce the possible consumption in CMOS by Reduction Of switching Activity

Ahlam Mahmoud Mahmoud<sup>1</sup>

(Received 1 / 3 / 2018. Accepted 2 / 5 / 2018)

#### $\Box$ ABSTRACT $\Box$

This research aims to reduce the possible consumption in CMOS digital circuit type and to develop new methods in this area and get the results of a new process applicable in the field of the development of integrated electronic devices of high integration VLSI, has been in this study the possible reduction of consumer dynamic by Reduction Of switching Activit where the researcher changed the architecture of digital circuit on the possible consuming, and she used different combinations of the circuit.

the researcher got good results in a manner using the Matlab simulation program where she got reduction of 10%, which helps us to achieve high standards in the design of integrated circuits.

**Key Words:** switching Activity- reduce the possible consumption

<sup>&</sup>lt;sup>1</sup> Master in Electronics and communications Engineering- Faculty of ... Engineering-Tishreen University-Lattakia,

#### مقدمة:

إن أسباب اللجوء إلى التصميم منخفض الاستطاعة ظهور الأنظمة المحمولة وتزايد الحاجة إليها مثل دفاتر Mobile Telecommunication وأجهزة الاتصال المحمولة Notebook Computers ولما كان الاعتماد Equipments والمساعدات الشخصية الرقمية Equipments والمساعدات الشخصية الرقمية عليها في الحياة اليومية ينمو بشكل كبير كان لابد من تأمين مصادر تغذية كهربائية لها بأقل ما يمكن من استهلاك الاستطاعة ونشر للحرارة، وبدوام أكبر لبطارية التغذية مع الحفاظ على الأداء العالي لهذه الأجهزة من حيث كمية المعلومات المختزنة وسرعة المعالجة. [1]

لذلك نحتاج إلى التصميم بأقل استهلاك للاستطاعة في الأنظمة الرقمية عالية الأداء والتي تتطلب كثافة عالية للشرائح المتكاملة IC ، وترددات عمل عالية مثل المعالجات الصغرية Microprocessors ودارات معالجة الإشارات الرقمية (Digital Signal Processing (DSP) ، وهذا يعني زيادة في استهلاك الطاقة وزيادة في نشر الحرارة، وبالتالي يتوجب علينا تبديد هذه الزيادة في درجة الحرارة حتى المستوى المقبول عن طريق التغليف Packaging أو التبريد Cooling مما يزيد من كلفة الأجهزة الإلكترونية.

#### مشكلة البحث:

تعتبر وثوقية الأنظمة عالية الاندماج VLSI مسألة هامة تشير إلى الحاجة إلى التصميم منخفض الاستطاعة، فهناك علاقة متبادلة بين تبديد الاستطاعة العظمى للدارات الرقمية والوثوقية، مثل حدوث ظاهرة هجرة الإلكترونات في أنصاف النواقل Electromegration وظاهرة الإجهاد الحراري الذي يتسبب للشريحة وعلاقته بالوثوقية. [2] وتشمل المنهجيات المستخدمة من أجل تحقيق استهلاك طاقة منخفض في الأنظمة الرقمية عدة مجالات تمتد من التصميم على مستوى الخوارزمية.

## أهمية البحث وأهدافه:

تعتبر دارة العاكس CMOS Inverter البنية الأساسية للدارات المتكاملة نوع CMOS والتي تتكون من البوابات NAND و NAND و OR و OR و OR و OR و العاكس يكفي لتقييم وحساب الاستطاعة المستهلكة في دارة العاكس يكفي لتقييم وحساب الاستطاعة المستهلكة في دارة متكاملة عالية الاندماج.

## منهجية البحث:

لكي نتمكن من تخفيض استهلاك الاستطاعة في نظام ما يتوجب علينا ما يلي: [3]

1-معرفة المنشأ الفيزيائي لهذه الظاهرة.

2-معرفة وقياس كمية الاستطاعة المستهلكة في كل جزء من النظام.

3-تحديد العناصر الأكثر أهمية في عملية استهلاك الاستطاعة.

لذلك تعتعمد منهجية البحث على انقاص فعالية التبديل لتخفيض الاستطاعة المستهلكة في بوابة العاكس CMOS على دارات متكاملة عالية الاندماج واستخدام بعض برامج المحاكاة مثل برنامج اله Matlab لنمذجة البوابات الرقمية وحساب الاستطاعة المستهلكة فيها وتحليل النتائج مع الاقتراحات والتوصيات.

#### الدراسات المرجعية في التصميم منخفض الاستطاعة

#### 1-دراسة ( S. Bobba and I. N. Hajj,2015) بعنوان :

#### **Maximum Leakage Power Estimation for CMOS Circuits**

في هذه الدراسة تم تخفيض الاستطاعة التسريبية إلى الحد الاعظمي في دارات CMOS من خلال إدخال عامل تحكم في مدخل الدارة وزيادة جهود العتبة للترانزستورات للحصول على تيار تسريب عكسي اصغري حيث قدمت الدراسة تخفيض يصل الى 2% من مجمل الاستطاعة الديناميكية. [4]

#### : بعنوان (Carsten Wulff and Trond Ytterdal, 2016) بعنوان -2

#### 0.8V 1GHz Dynamic Comparator in Digital 90nm CMOS Technology.

قدمت الدراسة طريقة لتصميم مقارن ديناميكي بجهد تغذية 0.8 فولط وتردد 1GHz بتكنولوجيا رقمية تصل الى دارات CMOS الرقمية 90nm حيث بينت هذه الدراسة ان الجهد المنخفض والاستطاعة المنخفضة والسرعة العالية للدارات التشابهية مناسبة للعمل بتكنولوجيا CMOS المقاسة بالنانو والمقارن الديناميكي يستهلك كحد أقصى 222Mw عند تردد ساعة 1GHz مع مكثفة حمل بسعة 100fF عند جهد تغذية يصل 0.8V التي هي اصغر من النتائج المقارنة. [5]

#### ( Prentice Hall, 2017) حراسة -3

#### Low Power Design in CMOS

قدمت هذه المقالة دراسة عن طرق تصميم الاستطاعة المنخفضة في دارات من خلال تخفيض تيار الدارة القصيرة وزيادة إشارات الدخل والخرج من خلال زيادة ازمنة الصعود والهبوط وزيادة جهود العتبة للترانزستور حيث تم التخفيض الى قيمة تيار دارة قصيرة 0.05 ميلى امبير وجهد عتبة 0.8. [6]

#### 4- دراسة (Ireneusz Brzozowski, Andrzej Kos,2016 ) بعنوان :

#### Minimisation of Power Consumption in Digital Integrated Circuits

#### by Reduction of Switching Activity.

قدمت هذه الدراسة طريقة لتخفيض استهلاك الاستطاعة الديناميكية في الدارات المتكاملة الرقمية بتخفيض فعالية التبديل من خلال حذف المداخل العاكسة وتحليل الدارة باستخدام قوانين ديمورغان حيث وصلت الى تخفيض يصل الى 6% من الاستطاعة المقارنة معها. [7]

#### اختلاف الدراسة الحالية عن الدراسات السابقة:

لقد تناولت الدراسات المرجعية تخفيض الاستطاعة المستهلكة الديناميكية من عدة جوانب أهمها: البحث في تخفيض جهد التغذية – التخفيض التدريجي لتردد العمل – تخفيض الاستطاعة التسريبية – تخفيض السعات الطفيلية – تخفيض استطاعة الدارة المقصورة – تخفيض استطاعة التبديل، ولكن سعى هذا البحث لتخفيض الاستطاعة المستهلكة الديناميكية بتخفيض فعالية التبديل حيث تم تغيير البنية الهندسية للدارة الرقمية ، واستخدم تراكيب مختلفة للدارة.

## الإطار النظري البحث:

## مفهوم الاستطاعة المستهلكة الديناميكية:

تعتبر دارة العاكس CMOS Inverter البنية الأساسية للدارات المتكاملة نوع CMOS والتي تتكون من البوابات NAND و NOR و OR و OR، ولذلك فإن دراسة وحساب الاستطاعة المستهلكة في دارة العاكس يكفي لتقييم وحساب الاستطاعة المستهلكة في دارة متكاملة عالية الاندماج.

هناك عدة مصادر لاستهلاك الطاقة في الدارات المتكاملة الرقمية MOS وجميعها تنضوي تحت نوعين رئيسيين هما: 1-استطاعة مستهلكة ساكنة Static Power Dissipation: هي الاستطاعة المستهلكة عند تواجد الدارة أو البوابة المنطقية في أحدى الحالتين المنطقيتين (1) أو (0). وتحصل هذه الاستطاعة عادة في درات NMOS و CMOS-استطاعة مستهلكة الديناميكية هي الاستطاعة المستهلكة الديناميكية هي الاستطاعة المستهلكة عند انتقال عقدة الخرج لدارة العاكس من حالة منطقية ما إلى الحالة المنطقية الأخرى.

كما هو معلوم ان الاستطاعة المستهلكة الديناميكية في دارة العاكس CMOS تتشأ وجود السعات الطفيلية في عقدة الخرج.

ان القيمة المختزنة في سعة عقدة الخرج  $C_{OUT}$  المشحونة الى الجهد  $V_{DD}$  تعطى بالعلاقة الشهيرة التالية:  $E=rac{1}{2}\,C_{OUT}.V_{dd}^2$  وبما ان جهد خرج العاكس يغير حالته مرتين بين فتح وإغلاق نجد أن الاستطاعة المستهلكة خلال نصف دور تعطى بالعلاقة التالية:

$$f_{clk}=rac{1}{T}$$

حيث أن T هو دور نبضات القدح المطبقة على الدخل P حيث أن P حيث أن T حيث أن حيث الدخل

حيث ان  $f_{clk}$  هو تردد نبضات القدح وبالتعويض نحصل على العلاقة:

$$P_D = C_{OUT}.V_{dd}.f_{clk}$$

هناك عدة مصادر للاستطاعة المستهلكة الديناميكية في دارات CMOS وتقسم إلى ثلاثة مصادر رئيسية هي [8]: 1-استطاعة مستهلكة ديناميكية أثناء التبديل Switching Power Dissipation.

2-استطاعة مستهلكة ديناميكية في الدارة القصيرة Short Circuit Power Dissipation.

.Leakage Power Dissipation استطاعة مستهلكة ديناميكية تسريبية-3

4- استطاعة مستهلكة ساكنة Static Power Dissipation.

#### الاستطاعة المستهلكة الديناميكية التبديلية:

تتم حادثة التبديل Switching عند انتقال Transition عقدة الخرج من الجهد (0) إلى الجهد Switching عند التجرار أثناء الانتقال طاقة من منبع التغذية لشحن مكثقة الخرج  $C_{out}$  عبر الترانزستور PMOS فتسحب قدرة من منبع التغذية ، يسمى هذا الانتقال بالمستهلك للطاقة Power Consumption Transition . نصف هذه القدرة يبدد كحرارة في الترانزستور PMOS والنصف الآخر يخزن في المكثقة المذكورة، والطاقة المبددة أثناء الانتقال تكون مستقلة نسبياً عن الوظيفة المنطقية المنفذة. [9]

وأيضاً هناك انتقال آخر لعقدة الخرج من الجهد  $V_{DD}$  إلى الجهد (0) يرافقه تغريغ لشحنة المكثفة عبر الترانزستور NMOS إلى الأرضي وتبديد الاستطاعة المخزونة على شكل حرارة.

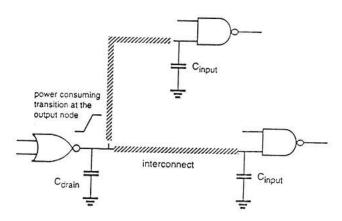

لتوضيح الاستطاعة المستهلكة الديناميكية أثناء التبديل نأخذ الدارة المبينة في الشكل(1) [10].

الشكل رقم (1) بوابة NOR تقود بوابتي NAND عبر خطوط وصل بينية.

التالية: الحمل السعوي من السعات التالية:  $C_{Load}$  عند عقدة الخرج للبوابة القائدة (NOR) يتكون من السعات التالية:

D بين المصرف Junction بين المصرف D وهي تتشكل من السعات الطفيلية للمتصل Substrate بين المصرف D والأساس Substrate وتتناسب قيمتها خطياً مع مساحة المتصل.

$C_{Interconnect}$  Interconnect Capacitors وتنتج عن خطوط التوصيل بين البوابات وهي المركبة السعوية الغالبة على السعات الأخرى للترانزستورات الحقلية وخاصة في مجال الترددات الميكروية.

$C_{input}$  وتتشأعن سعات الأوكسيد المتشكلة بين البوابة وطبقة الأساس وتتحدد قيمتها بمساحة البوابة .

## التمثيل العام لبوابة CMOS لحساب الاستطاعة المستهلكة التبديلية:

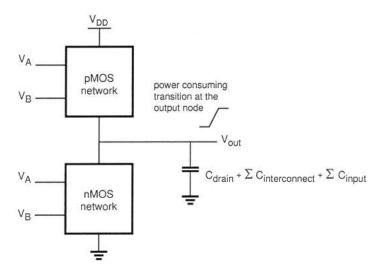

يبين الشكل(2) تمثيل عام لبوابة CMOS من أجل حساب الاستطاعة المستهلكة التبديلية وهي تتكون عادة من شبكة NMOS وشبكة PMOS تابعة لها.

الشكل رقم (2)-التمثيل العام لبوابة CMOS لحساب الاستطاعة المستهلكة أثناء التبديل.

سعة الحمل الإجمالية

$$C_{Total}$$

موصولة إلى عقدة الخرج وتساوي: [11]  $C_{Total} = C_{Drain} + \sum C_{Interconn xct} + \sum C_{Input}$

متوسط استهلاك الاستطاعة لبوابة واحدة نوع CMOS (عاكس Inverter) مقادة بواسطة جهد دوري نبضي ذي زمني صعود وهبوط صفريين (معدومين) وذلك من خلال الطاقة اللازمة لشحن سعة الحمل إلى الجهد  $V_{DD}$  وتفريغ سعة الحمل الإجمالية إلى مستوى الأرضي (صفر فولت) خلال دور واحد يعطى بالعلاقة التالية [12]:

$$P_{avg} = \frac{1}{T} \left[ \int_{0}^{T/2} V_{Out} \left( -C_{Load} \frac{dV_{Out}}{dt} \right) dt + \int_{T/2}^{T} \left( V_{DD} - V_{Out} \right) \left( C_{Load} \frac{dV_{Out}}{dt} \right) dt \right],...(2)$$

الحد الأول يمثل شحن المكثفة Charge عبر PMOS والحد الثاني يمثل تفريغ المكثفة Discharge عبر NMOS. بحل هذا التكامل نحصل على تقدير جيد ومعروف في متوسط استهلاك الاستطاعة الديناميكية أثناء التبديل في دارات CMOS الرقمية كما يلى:

$$P_{avg} = \frac{1}{T} C_{Load} \times V_{DD}^2, \dots (3)$$

وبتعويض التردد:

$$P_{avg} = C_{Load} \times V_{DD}^2 \times F_{clk}, \dots (4)$$

نلاحظ من خلال المعادلة أن الاستطاعة المستهلكة الديناميكية التبديلية مستقلة عن خواص الترانزستور وأبعاده الهندسية، وهي مستقلة أيضاً عن أزمنة صعود وهبوط إشارة الدخل طالما أن جهد الخرج ينتقل بين الصفر والجهد  $(V_{DD})$ .

إن التحليل السابق لتبديد الطاقة الديناميكية التبديلية يعتمد على فرضية أن عقدة الخرج لبوابة CMOS تخضع لانتقال مستهلك طاقة وحيد وهو الانتقال من (0) إلى الجهد ( $V_{DD}$ ) في كل دور ساعة. وهذه الفرضية ليست دائماً صحيحة، حيث أن معدل انتقال العقدة يمكن أن يكون أصغر من معدل نبضات الساعة بحسب نوع المنطق المستخدم، ولذلك فمن أجل تمثيل أفضل لاستهلاك الاستطاعة التبديلية سوف ندخل بارامتر جديد وهو معدل انتقال عقدة الخرج  $\alpha_T$  وهو العدد الفعال لانتقالات الجهد المستهلك للطاقة خلال دورة ساعة ليصبح متوسط استهلاك الطاقة التبديلية كما يلي [13]:

$$P_{avg} = \alpha_T \cdot C_{Load} \cdot V_{DD}^2 \cdot F_{clk}, \dots (5)$$

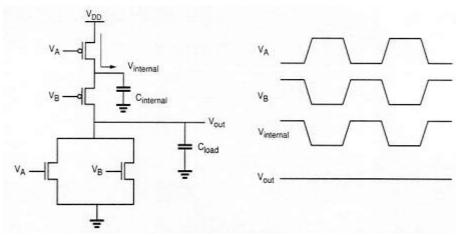

في الحقيقة يمكن أن تخضع عقدة داخلية في دارة منطقية معقدة لعدة انتقالات بينما يبقى جهد عقدة الخرج بدون تغير، وهذه الانتقالات الداخلية تساهم في زيادة استهلاك الاستطاعة للدارة يمكن توضيح هذا المفهوم بالاعتماد على الشكل(3).

الشكل رقم (3)-التبديل في العقد الداخلية لبوابة NOR بمدخلين

يمثل الشكل المذكور بوابة NOR نوع CMOS بمدخلين و نلاحظ من الشكل ومن المخططات الزمنية لجهد العقدة الداخلية  $V_{out}$  وجهد عقدة الخرج  $V_{out}$  أن العقدة الداخلية تخضع لعدة انتقالات جزئية وبدون أن يتغير جهد عقدة الخرج، وبالتالي يحدث استهلاك إضافي للطاقة. يمكن لجهد العقدة الداخلية أن تتأرجح بمقدار جهد الدخل  $V_{in}$  أقل من جهد التغذية  $V_{out}$  ، وفي هذه الحالة نكتب:

$$P_{avg} = \sum_{i=1}^{Number.Of.Nodes} (\alpha_{Ti} \cdot C_i \cdot V_{in}) \cdot V_{DD} \cdot F_{CLK}, \dots (6)$$

حبث أن:

$\cdot^i$  السعة الطفيلية الخاصة بالعقدة الداخلية :  $C_i$

. i معدل انتقال العقدة الداخلية :  $lpha_{Ti}$

التبديل. NumberOfNales  $\sum_{i=1}^{NumberOfNales} (lpha_{Ti} \cdot C_i \cdot V_{in})$  . هو كمية الشحنة الكلية المستجرة من منبع التغذية أثناء التبديل.

تبين العلاقة (6) أنه يمكن تخفيض الاستطاعة المستهلكة الديناميكية التبديلية بعدة طرق وهي:

$V_{DD}$  إنقاص جهد التغذية $^{-1}$

$C_{Load}$  الحمل في الحمل السعة الطفيلية في الحمل -2

$V_i$  انقاص جهد الدخل في كل عقدة-3

$\alpha_T$  الانتقال معدل الانتقال -4

$F_{clk}$  إنقاص تردد الساعة -5

#### إنقاص فعالية التبديل:Reduction Of switching Activity

يمكن تخفيض فعالية التبديل في الدارات المتكاملة الرقمية CMOS بعدة طرق نذكر منها:

1-استخدام أمثلية الخوارزمية. وذلك بالاختيار الصحيح للمخطط الطوبولوجي للدارة المنطقية.

2- أمثلية أسلوب البناء (تركيب الدارة).

3- الاختيار المناسب للأداء المنطقى.

4- أمثلية مستوى الدارة.

5-إنقاص السعة التبديلية Reduction of Switched Capacitance

6-تخفيض الإشارات الزائفة reduction of glitches في الخرج.

7-استخدام إشارات ساعة مبوبة Gated Clock Methode

تعتمد أمثلية الخوارزمية بشكل كبير على نوع التطبيق وعلى مواصفات المعطيات بشكل أفضل ليمكن من الحصول على مجال ديناميكي أفضل ، الترابط، إحصاءات نقل المعطيات، وتستخدم بعض التقنيات في ذلك مثل المعالجة الرقمية للإشارة DSP. وإن الاختيار المناسب للأداء المنطقي يعني اختيار التابع المنطقي الذي يعطي أقل تغيرات للخرج مع تغير إشارات الدخل.

يمكن إنقاص السعة التبديلية بإجراءات على عدة مستويات: [14]

1-إجراءات على مستوى النظام.

2-إجراءات على مستوى الدارة .

3-إجراءات على مستوى التصميم الفيزيائي للعنصر.

#### 1- الإجراء على مستوى النظام:

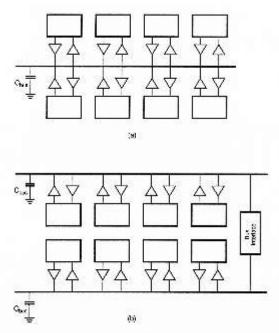

كأن نقوم بالحد من استخدام الموارد المشتركة (الممرات المشتركة) للنظام لتقليل السعة التبديلية، حيث نستبدل الممر المشترك المشترك الوحيد في تركيب الممر العام لمعطيات التمرير كما هو موضح في الشكل(4).

في الحالة الأولى: حالة الممر المشترك ستنتج سعة ممر كبيرة بسبب:

1- العدد الكبير من دارات القيادة والمستقبلات المساهمة بنفس معدل الإرسال.

2-السعة الطفيلية لخط الممر الطويل.

مما ينتج استهلاك طاقة كبير.

أما في الحالة الثانية: حالة استخدام الممر العام يقسم الممر العام إلى عدد من الممرات الفرعية لمعالجة معطيات الإرسال بين النماذج المتجاورة، ونحصل على سعة تبديلية للممر الفرعي أصغر منها في حالة الممر العام، ولكن ذلك يزيد من مساحة ممرات التوصيل على الشريحة.

الشكل رقم (4) -الممر العام لمعطيات التمرير

#### - الإجراء على مستوى الدارة:

لإنقاص سعة الحمل تستخدم بوابات النقل Transfer Gates بدلاً من بوابات CMOS التقليدية لأنها تحتوي على عدد أقل من الترانزستورات، ولما كانت بوابات التمرير تحتاج إلى إشارات تحكم متتامة فيتم استخدام المنطق المزدوج لتجنب جميع الإشارات المتتامة.

بالتالي يلزم شبكتي تمرير ترانزستورين من النوع NMOS وتأرجح جهد وبوابات عزل الخرج، وهذا يقلل من ميزات استخدام بوابة النقل.

## 3- الإجراء على مستوى التصميم الفيزيائي:

أثناء التصنيع نحاول تشكيل ترانزستورات بأبعاد أصغرية مما يقلل من سعات الانتشار والسعة الطفيلية للبوابة ،إنما هذا يؤثر على العمل الديناميكي للدارة ، ولذلك نحاول التوفيق بين العمل الديناميكي وتبديد الاستطاعة.

## النتائج والمناقشة:

## تخفيض الاستطاعة المستهلكة الديناميكية بتخفيض فعالية التبديل:

يعرف معدل انتقال العقدة  $\alpha_T$  على أنه العدد الفعال لانتقالات الجهد المستهلك للطاقة من قبل سعة الحمل في الخرج خلال دورة ساعة واحدة .

نتعلق فعالية النبديل بالوظيفة المنطقية البوليانية التي تؤديها الدارة، وبالعائلة المنطقية، وباحتمالات إشارات الدخل أن تكون بالحالة المنطقية ( $^0$ ) أو ( $^1$ ). وفي الحالة العامة يوصف انتقال الخرج المستهلك للطاقة كتابع لعدد الأصفار في عمود الخرج بأنه الانتقال من الحالة المنطقية ( $^0$ ) إلى الحالة المنطقية ( $^0$ )، أي الانتقال من الحالة المنطقية ( $^0$ ) إلى الحالة المنطقية ( $^0$ )، أي الانتقال من الحالة المنطقية ( $^0$ ) المنطقية ( $^0$ ) إلى الحالة المنطقية ( $^0$ )، أي الانتقال من الحالة المنطقية ( $^0$ ) المنطقية ( $^$

وباستخدام هذا التعريف فإن فعالية التبديل للبوابة المنطقية يمكن أن يتم تقييمه بالتعبير التالي: [ 15]

$$A_i = \sum_i A_i = \sum_i 2 |F_i| |R_i|$$

حيث  $A_i$  هي فعالية التبديل الكلية للدارة. و  $A_i$  هي فعالية التبديل عند العقدة i تمثل مجموعة العوامل الأصغرية من الوظيفة المنطقية عند العقدة i ، و i تمثل العوامل العظمي.

على سبيل المثال لبوابة NAND بمدخلين حيث  $\begin{vmatrix} F & | & 3 \\ e & | & 3 \end{vmatrix}$ ، يتم تقييمها بـ 6 باستخدام التعريف السابق. فعالية التبديل عند عقد منفصلة تعتمد على العاملين السابقين على خرج العقدة. [ 16]

من التعریف السابق یتبین بأن العاکس یملك أعظم فعالیة تبدیل.اذلك فإن التقنیة الأساسیة لتخفیض فعالیة التبدیل هی بحذف العواکس التی تعتبر کمداخل. الطریقة الأساسیة هی بتجمیع(terms) العوامل السلبیة فی ثلاث متحولات أو أکثر وتطبیق قوانین دی مورغان لإنتاج تراکیب یمکن تطبیقها باستخدام بوابة NAND. علی سبیل المثال المثال  $\overline{XY} + \overline{X} + \overline{X}$  یمکن حذف العواکس باستخدام بوابة OR، کما یلی  $\overline{WXY}$  یمکن تحویلها إلی  $\overline{WXY} + \overline{X} + \overline{X}$ . ثلاث متحولات أو أکثر مع متحول سلبی واحد یمکن أن تتحول باستخدام قوانین دی مورغان کما یلی:  $\overline{W(X+Y)}$ .

لهذه الطريقة عدة سلبيات وهي:

إن تقييم فعالية التبديل باستخدام عدد صحيح يشير إلى مقدار فعالية التبديل وبالتالي مؤشر للاستطاعة المستهلكة (كما تمت الدراسة) يعتبر أمراً شبه مستحيل في مقارنة الدارات بسبب عدم وجود مرجعية قياسية يمكن أن تعتمد من أجل عمليات المقارنة.

فضلاً عن ذلك لا يوجد قيم حدية عليا لفعالية التبديل عند استخدام التعريف السابق على الرغم من أن الطريقة السابقة تقدم طريقة لتخفيض فعالية التبديل إلا أنها لا تقدم إجراء رسميا لتصميم الدارة مع تخفيض لفعالية التبديل. [17] هناك طريقة أخرى تتجاوز بعضا من سلبيات الطريقة السابقة وهي طريقة فصل العناصر [18]، وتقدم هذه الطريقة حلا لحذف العواكس وتضع قيما حدية لفعالية التبديل كمؤشر للاستطاعة المستهلكة.

طريقة فصل العناصر لتخفيض فعالية التبديل والتي تهدف إلى زيادة عدد مداخل البوابة. هي تقسم العناصر الأساسية إلى SOPأو POSأو POSأو معزية والتي يمكن أن تشارك شروطا أصغرية أو أعظمية في عملية الفصل. عملية التقسيم تجري بحيث يتم تقديم متحولات متكاملة جديدة. التقسيم يزيد عدد المتحولات في العناصر، لذلك زيادة عدد المداخل للبوابة يقلل مباشرة من فعالية التبديل. الطريقة المعروضة في (1)

لحذف المداخل العواكس تطبق في الوظيفة الناتجة. المثال التالي يشرح التقنية.

لنفرض الوظيفة التالية  $F = WZ + \overline{X}Z + \overline{W}X\overline{Y}$ . هنا سوف نراقب جزئيين، المتحولين الأساسيين المتشاركين بالشرط الأصغري.

احد هذه العناصر الأساسية يمكن تقسيمه لجعل هذه IMPLICATES غير متصلة. وفقا للإجراء المقدم في [2]، فإن أفضلية التقسيم تعطى إلى المتحول (المتحولات) التي تحوي متحول متمم واحد. هذا يعطينا الوظيفة:  $F = WZ + \overline{W}Z\overline{X} + \overline{W}X\overline{Y}$  القسمين الأخيرين اللذين يحويان متحولين متممين يمكن تحويلهما  $\overline{W} = WZ + \overline{W}Z\overline{X} + \overline{W}Z\overline{X}$  حاذفة المداخل العاكسة. [18]

فعالية التبديل المعرفة في (1) تم تعديلها في(2) لتكون مرضية للتعاريف الكلاسيكية بوضع قيم حدية للفعالية بحيث تكون قيمة الفعالية الأعظمية هي 1. فعالية التبديل عند العقدة تعرف بأنها احتمالات الانتقال للعقدة من 0 إلى 1 و من 1 إلى 0، حيث يعطى احتمالات الانتقال للعقدة كجداء احتمالات بقاء العقدة عند 0 و 1. لنفرض  $P_0$  هي من 1 إلى 0، حيث يعطى احتمالات الانتقال للعقدة كجداء احتمالات بقاء العقدة عند 0 و 1. لنفرض  $P_0$  هي  $P_1 = \frac{1}{|R|+|F|}$   $P_0 = \frac{1}{|R|+|F|}$   $P_0 = \frac{1}{|R|+|F|}$  من اجل بوابة NAND بمدخلين  $P_1 = \frac{3}{4}$  .

$P_{1-0}=\left(\frac{3}{4}\right)\left(\frac{1}{4}\right)=\frac{3}{16}$  والطاقة .  $P_{0-1}=\left(\frac{1}{4}\right)\left(\frac{3}{4}\right)=\frac{3}{16}$  . المناقشة على فعالية التبديل التي تمت في [2] من مصدر البطارية فقط عندما الخرج يشحن من 0 إلى 1. المناقشة على فعالية التبديل التي تمت في أخذت بعين الاعتبار الانتقال من 0 إلى 1.

الإجراء في [2] لا يأخذ بعين الاعتبار الحالة التي يكون فيها الدارة ذات فعالية التبديل الأصغرية منجزة مباشرة من تطبيق متعدد المستويات كما هو موضح:

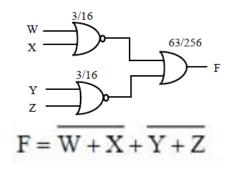

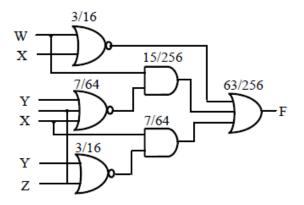

حيث أن فصل العناصر يزيد من عدد المستويات وبالتالي يزيد من قيمة فعالية التبديل.[ 19]و[ 20] لنفرض الوظيفة التالية  $\overline{\mathbf{F}} = \overline{\mathbf{W}} \overline{\mathbf{X}} + \overline{\mathbf{Y}} \overline{\mathbf{Z}}$ . هذا بشكل مباشر يطبق الى الشكل (10) باستخدام قوانين دي مورغان والتي تملك فعالية تبديل اصغرية لهذه الوظيفة. بتطبيق الخوارزمية المقدمة في [2] نلاحظ انه تم زيادة عدد المداخل كما هو مقترح. إلاأن فعالية التبديل أصبحت اكبر كما هو موضح بالشكل (10) مقارنة مع الشكل (11).

الشكل رقم (5) دارة تمثلي التابع

$$F = \overline{WX} + X\overline{YZ} + W\overline{X}\overline{YZ}$$

الشكل رقم (6) – دارة تمثي التابع

درسنا العوامل المؤثرة على تخفيض فعالية التبديل وهي:

حذف المداخل العاكسة.

زيادة عدد المداخل.

درسنا كيفية تاثير هذه العوامل على فعالية التبديل.

إن فعالية التبديل هي تابع لعدد الواحدات والأصفار . فعالية التبديل تكون أصغرية عندما الفرق بين |R|,|F| تكون اعظمية عندما |R|=|F|. تابعا بـ |R|=|F| متحول سوف يملك |R|=|F| احتمالا كليا من تراكيب الدخل.

لنفرض x تمثل قيمة |F|. عندها قيمة |R| ستكون x - 1.[ [21]

$$p_1 = x/2^k$$

و  $p_0 = (2^k - x)/2^k$  عندها يكون

الاستطاعة المستهلكة بسبب فعالية التبديل تعطى بالعلاقة التالية: (جداء الاحتمالين)

$$p_{0-1} = x(2^k - x)/2^{2k}$$

لحل المعادلة نجعلها مساوية للصفر من اجل قيمة X.

$$x(2^k - x)/2^{2k} = 0$$

$$x = 2^k/2$$

من خلال هذه المعادلة فإن فعالية التبديل تكون أعظمية عندما عدد الأصفار والواحدات للتابع يكون متساويا . لكون العاكس يحوي نفس عدد الأصفار والواحدات لذلك فعالية التبديل للعاكس أعظمية.

كذلك فإن فعالية التبديل هي تابع لعدد المداخل للبوابة. بوابة بعدد مداخل اقل سوف تملك فعالية تبديل أعظمية مقارنة مع بوابة بعدد مداخل اكبر. باستثناء  $\frac{XOR \& XNOR}{XNOR}$  والتي تملك فعالية تبديل تساوي  $\frac{1}{2}$ . لنفرض بوابات مع بوابة بعدد مداخل اكبر. باستثناء  $\frac{1}{2}$  مدخل، عندها ستكون  $\frac{1}{2}$  اما  $\frac{1}{2}$   $\frac{1}{2}$  مدخل، عندها ستكون  $\frac{1}{2}$  اما  $\frac{1}{2}$   $\frac{1}{2}$

وبالتالي  $p_0=1/2^i$  وبالتالي الطاقة المستهلكة بسبب فعالية التبديل هي  $p_1=(2^i-1)/2^i$  وبالتالي الطاقة المستهلكة بسبب فعالية التبديل هي  $p_0=1/2^i$  وبالتالي الطاقة المستهلكة بسبب فعالية التبديل هي وبالتالي الطاقة المستهلكة بسبب فعالية التبديل هي  $p_0=1/2^i$  وبالتالي الطاقة المستهلكة بسبب فعالية التبديل هي التبديل الطاقة المستهلكة بسبب فعالية التبديل هي المستهلكة بسبب فعالية التبديل الطاقة التبديل التبد

يمكن التعبير عن هذه المعادلة بالشكل التالي:

$$p_{0\to 1} = \big(\frac{_1}{_{2^i}} \text{-} \frac{_1}{_{2^{2i}}}\big)$$

نلاحظ بأن الاحتمال هو تابع لعدد مداخل البوابة، انه يتناقص عندما يزيد عدد المداخل والعكس بالعكس.

لذلك فإن عدد المداخل للبوابة يعتبر عاملا هاما في تصميم الدارة منطقيا من اجل تخفيض فعالية التبديل.

4- تصميم فعالية تبديل أصغرية:

سنقدم طريقة لتصميم الدارات المنطقية مع الأخذ بعين الاعتبار تخفيض فعالية تبديل. الهدف الأساسي هنا هو حذف المداخل العاكسة، لذلك سنقوم بفرض كافة التعابير الممكنة.

كذلك سنقوم بدراسة أثر عدد المداخل على فعالية التبديل الكلية كذلك اختيار مؤشر لتصميم الدارة المناسبة بفعالية تبديل أصغرية مع الأخذ بعين الاعتبار عدد مستويات التطبيق.

لنفرض تابعا بـ n متحول:

بداية إذا كانت كافة التراكيب في التابع سلبية أو غير سلبية عندها مباشرة نقول أن فعالية التبديل أصغرية.

ثانيا إذا كان تركيبان أو أكثر ضمن التابع يحويان متحولات غير سلبية مشتركة مع متحول سلبي واحد مختلف، عندها يمكن دمج التراكيب إلى تطبيق متعدد المستويات باستخدام طريقة NAND/NOR

$$W\overline{X} + W\overline{Y} = W(\overline{X} + \overline{Y}) = W(\overline{XY})$$

کمثال

التراكيب التي تحوي ثلاث متحولات أو أكثر بعنصر سلبي واحد أو أكثر يمكن حذف عواكسها باستخدام طرق متعددة المستويات (استخدام أكثر من بوابة).

## الخوار زمية المقترجة:

الحصول على f<sub>SOP</sub>&f<sub>POS</sub> للتابع المعطى.

إذا كان كل من  $f_{\text{SOP}} \& f_{\text{POS}}$  لا يحوي على تركيب المتحولين مع عنصر سلبي عندها يكون الحل مثالي. وعندها نختار الحل الافضل بين الخيارين  $f_{

m SOp}\&f_{

m pos}$  والذي يقابل فعالية تبديل اصغرية. حساب فعالية التبديل يتم للتطبيق متعدد المستويات. نغلق الخوارزمية

والا، نعدل المجموعة في K-map التي تمثل تركيب المتحولين (بإضافة متحول واحد يظهر في الصيغة السلبية). بحيث أن المتحول (المتحولات) الإضافية يمكن أن تضاف إلى التعبير، حيث يتم تزويد هذا المتحول بحيث أن العدد الكلى للمجموعات في k-map يبقى ثابتا.عندها المتحولات المتممة يمكن حذفها بتطبيق متعدد المستويات الخيار النهائي في اختيار التصميم المناسب يتم بعد حساب فعالية التبديل للتراكيب المختلفة

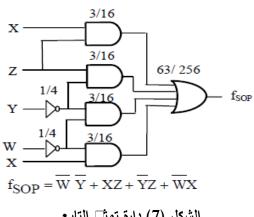

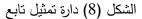

الشكل (7) دارة تمثلي التابع

$F = (\overline{W} + \overline{Y}) + XZ + \overline{X}\overline{Y}Z + \overline{W}X\overline{Z}$

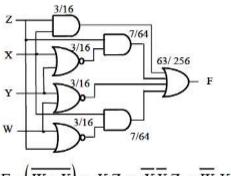

الشكل (9) دارة تمثيل تابع

حساب فعالية التبديل للمثال السابق في التطبيقات الثلاثة:

| الشكل 1 | X1=[1/4, 1/4, 3/16, 3/16, 3/16, 3/16, 63/256]         |

|---------|-------------------------------------------------------|

| الشكل 2 | X2 = [7/64, 7/64, 3/16, 3/16, 3/16, 3/16, 63/256]     |

| الشكل 3 | X3 = [15/256, 15/256, 3/16, 3/16, 3/16, 3/16, 63/256] |

فعالية التبديل في الشكل (9) وخلال المستوى الأول هي اقل وبشكل واضح من الشكلين (7)و (8). انخفضت من 0.25 حتى 0.06 للمستوى الأول

نلاحظ من خلال الدراسة ومن النتائج التجريبية وتطبيق الخوارزمية على مجموعة من الدارات المختلفة التركيب نجد أن عملية إضافة المتحولات تتوقف عندما يصبح عدد العناصر في أحد التراكيب مساوياً لعدد المتحولات الكلى.

شملت الدراسة دارات بخمسة مداخل كما تم تطبيق الخوارزمية المقترحة وتبين الحصول على نفس النتائج.

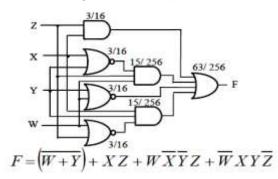

مقارنة عدد المداخل الناتجة مع فعالية التبديل كما في الشكل التالي: حيث تتناقص فعالية التبديل مع زيادة عدد المداخل كما هو مبين في الشكل (10) الآتي:

عدد مداخل البوابة الشكل (10) يبين العلاقة بين فعالية التبديل وعدد مداخل البوابة

#### الاستنتاجات والتوصيات:

#### الاستنتاجات:

تم مقارنة تصميمين (4 & 6) متحولات من خلال تطبيق هذه الخوارزمية ولمرحلتين متتاليتين والنتائج كما يلي:

| فعالية التبديل | المستويات | عدد المداخل | عدد التراكيب | عدد المتحولات |                 |

|----------------|-----------|-------------|--------------|---------------|-----------------|

| 1.5            | 3         | 14          | 4            | 4             | المرحلة الاولى  |

| 1.2            | 3         | 16          | 4            | 4             | المرحلة الثانية |

|                 | عدد المتحولات | عدد التراكيب | عدد المداخل | المستويات | فعالية التبديل |

|-----------------|---------------|--------------|-------------|-----------|----------------|

| المرحلة الاولى  | 6             | 5            | 18          | 3         | 1.7            |

| المرحلة الثانية | 6             | 5            | 21          | 3         | 1.3            |

1-تم تقديم طريقة لتخفيض الاستطاعة الديناميكية المستهلكة في دارات الـ CMOS بطريقة إنقاص فعالية التبديل. 2-باستخدام هذه الطريقة تم التوصل إلى تخفيض الاستطاعة بحوالي 10% من خلال تغيير البنية الهندسية للدارة. 3-يمكن زيادة هذه النسبة (نسبة تخفيض الاستطاعة) من خلال استخدام تراكيب مختلفة.

4-تبين من خلال هذا البحث أن هناك زيادة في تخفيض فعالية التبديل عند زيادة عدد المداخل بالإضافة إلى حذف العواكس بنسبة تصل حتى 30%.

#### التوصيات:

1-يمكن تخفيض الاستطاعة المستهلكة الديناميكية في الدارات الرقمية CMOS من خلال تخفيض تيارات التسريب العكسية ضمن البنية وذلك من خلال التصميم الأمثل للبنية التكنولوجية لدارة العاكس (تكنولوجياً).

2-يمكن تخفيض الاستطاعة المستهلكة الديناميكية في الدارات الرقمية CMOS بتخفيض سعة الخرج للبوابة والذي من شأنه أن يخفض من فعالية التبديل المستهلك للطاقة (تكنولوجياً).

3-العمل على تطبيق عدد متحولات أكبر في المداخل في حالة الدارات المتكاملة عالية الاندماج.

4-استخدام تراكيب بوابات منطقية اخرى (NOR-NAND) من اجل عملية تغيير البنية الهندسية للدارة .

#### المراجع:

- [1] NAJM, F. "A survey of power estimation techniques in VLSI circuits," *IEEE Transactions on VLSI Systems*, vol. 2, December2013,pp. 446-455

- [2] HAYES & Horowitz." Field-E\_ect (FET) transistors" .2013,(pp 142-162 and 244-266), Spring .

- [3] OLEVEIRA Pinto, R.L.; Schneider, M.C; and Montoro, C.G. Sizing of MOS transistors for amplifier design. ISCAS, 2013.

- [4] ATHAS, W.C., L. Swensson, J.G. Koller and E. Chou. "Low-power digital systems based on adiabatic- switching principles," IEEE , *Transactions on VLSI Systems*, vol. 2, 2013, pp. 398-407.

- [5] HASAN, M. H; Shen, H.P; . Allee, D.R; and Pennell ,M. A behavioral model of a 1.8-V flash A/D converter based on device parameters. *IEEE Trans. on computer-aided design of integrated circuits and systems*, 2014, vol 19(1): p 69-82.

- [6] TIRI et al C. A dynamic and differential CMOS logic with signal independent power consumption to withstand differential power analysis on smart cards, *Proc. ESSCIRC* 2002, *Florence, Italy*, September , 2014, pp 403–406.

- [7] JESPERS, P.G.A.MOS-AK "workshop Sizing CMOS circuits by means of the gm/,*ID* methodology and a compact model ",Dec 13, 2014.

- [8] PU, Y.; Pineda de Gyvez ,J; Corporaal and Y. Ha. "An ultra-low-energy/frame multi-standard JPEG coprocessor in 65nm CMOS with sub/near-threshold power supply", *in IEEE Int. Solid-Stace Circ.* Conf., 2014, pp. 146-147.

- [9] HOROWITZ, M.; Indermaur T., and Gonzalez, R. "Low-Power Digital Design", *IEEE Symposium on Low Power Electronics*, 2014, pp.8-11.

- [10] RABAEY, J.M. and Pedram, M. ed . Low Power Design Methodologies. Norwell, MA: *Kluwer Academic Publishers*, 2015, pp.153.

- [11] CHANDRAKASAN, A.P. and Brodersen, R.W. Low Power Digital CMOS Design, Norwell, MA: *Kluwer Academic Publishers*, 2015.

- [12] Rabaey, J.M. and Pedram, M. ed. Low Power Design Methodologies, Norwell, MA: *Kluwer Academic Publishers*, 2015.

- [13] PANT. P.; DE,V. K; and Chatterjee, A. Simultaneous Power Supply, Threshold Voltage, and Trabsistor Size Optimization for Low-Power Operation of CMOS Circuits, IEEE Trans. on VLSI Systems, vol. 6, no. 4, December 2015.

- [14] GUYOT, A.; Abou-Samara, S. *Power Consumption in Digital Circuits*, 3rd International Conference on ASIC (ASICON '98), Beijing, China, 20-23 October, 1998.

- [15] BRATEK, P; A. Kos, Complex Optimisation of Topology of VLSI Circuits with Self-Organising Neural Nets, Proc, 2015.

- [16] MICHELI, G. De. Synthesis and Optimisation of Digital Circuits, McGraw-Hill, 2016.

- [17]LUBA,T. *Multi-Level Logic Synthesis Based on Decomposition*, Microprocessors and Microsystems, Vol. 18, No 8, 2016, pp.429-437

- [18] JOZWIAK, L. General Decomposition and its Use in Digital Circuits Syntesis, VLSI Design, *Specjal Issue on Decompositions in VLSI Design*, Vol. 3, No 3-4, 2016 pp.225-248 [19] WANG, Ch. Roy, K. An Activity-Driven Encoding Scheme for Power Optimisation in Microprogrammed Control Unit, *IEEE Trans. on VLSI Systems*, vol. 7, no. 1, March, 2017.

- [20] LAKSHMINARAYANA, G.; Raghuanthan, A.; N. Jha, Dey, S. Power Management in High-Level Synthesis, *IEEE Trans. on VLSI Systems*, vol. 7, no. 1, March, 2017.

- [21] TIRI et al, C. A dynamic and differential CMOS logic with signal independent power consumption to withstand differential power analysis on smart cards, *Proc. ESSCIRC* 2002, *Florence, Italy*, September, 2017, pp. 403–406.

- [22]BAKER,R. J. "CMOS Circuit Design, Layout, and Simulation," 3rd edition, Wiley-IEEE Press, Sep 2017.